概念

特点

时序电路任意时刻的输出信号不仅取决于当时的输入信号,还与初始状态及以前的输入有关。时序电路通常包括组合电路和存储电路两部分,另外包含输出到输入的反馈回路。

分类

时序电路根据时钟不同,可以分为同步时序电路和异步时序电路,根据输出信号的特点,可以分为米利型(Meely)和摩尔型(Moore)。

- 米利型:F(X,Q),输出信号取决于状态和输入;

- 摩尔型:F(Q),输出信号仅取决于状态。

表示方法

逻辑方程(驱动方程、状态转移方程、输出方程)、状态转移表、状态转移图、时序图等。

一般时序逻辑电路的分析与设计

同步与异步

同步和异步的概念是指电路的变化与时钟脉冲是否同步。

时序逻辑电路的分析

同步时序逻辑电路的分析步骤如下:

- 列出各级触发器的驱动方程;

- 将驱动方程代入触发器特性方程,得到转移方程;

- 列出输出方程;

- 由输出方程和状态转移方程,列出状态转移表,画出状态转移图和波形图;

- 总结概括电路的逻辑功能。

异步时序逻辑电路的分析需要注意各级触发器的CP时钟源。

自启动

若偏离态能在脉冲信号作用下自动转入到有效序列,则电路可以自启动,否则不能自启动。

时序逻辑电路的设计

同步时序逻辑电路的设计步骤如下:

- 根据实际需要建立状态转移图和状态转移表;

- 原始状态化简;

- 状态编码;

- 选择触发器类型;

- 检查电路自启动,绘制电路图。

异步时序逻辑电路的设计需要注意触发器时钟信号的选择,选取原则:

- 触发器状态需要翻转的时候,必须要有时钟信号输入;

- 触发器状态不需要翻转的时候,多余的时钟信号越少越好。

常用时序逻辑电路

计数器

计数器有多种实用功能,如计数、分频、定时、产生节拍脉冲、脉冲序列和数字运算等,故又称分频器。最大计数称为计数器的模,符号N。

计数器的分类:

- 根据脉冲方式分为:同步计数器、异步计数器;

- 根据逻辑功能分为:加法计数器、减法计数器、可逆计数器;

- 根据模值划分。

生活中常用集成计数器,主要有可逆计数、预置、清零、进位等功能。

74LS161

74LS161是4位同步二进制计数器,模为16。为同步预置数控制端,为异步清零端,CO为进位输出端。EP和ET为工作状态控制端,当EP为0,ET为任意态,CO保持;当ET为0,EP为任意态,CO为0。

计数器的扩展

设需要设计的模值为M,已有计数器模值为N。

当N>M时,可利用同步预置取M个状态(N-M到N-1),或者利用异步清零,取M+1(0到M,其中M是瞬间出现而后消失)。需要注意的是,对于异步清零法的设计,为了提高清零信号的可靠性,通常需要在清零信号前加一个基本RS触发器,如下所示:

在改进后的电路中,由基本RS触发器的R'端接计数器的清零端,R端作为进位输出端。

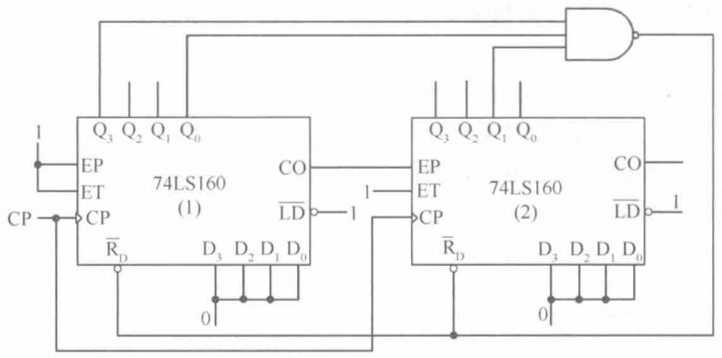

当N<M时,需要多片计数器级联。在设计任意模值计数器前,不妨试着分析已有的计数器级联电路。

由图可知,当片1输出为1001(9)且片2输出为0010(2)时,2片计数器同时异步清零,74LS160为模10计数,故整体电路模值为10×2+(9-1+1)=29。加1是因为0到n,计数n+1次;减1是因为异步清零,末态瞬间消失,所以这里最好也加上一个基本RS触发器,或者改用置数法实现。如下图所示(10×2+(8+1)=29)。

寄存器和移位寄存器

寄存器分为基本寄存器和移位寄存器,基本寄存器只能并入并出,移位寄存器可以在移位脉冲作用下依次逐位右移或左移,数据可以并入并出、并入串出、串入串出、串入并出。

一般来说,规定左为低位、右为高位,即,此时左移右移直观可见。

74LS194

74LS194是一款常见的集成式4位双向移位寄存器。

74LS195

74LS195具有JK输入,只能进行右移操作,端补位值遵循。

一般n位移位寄存器可以实现模值n的环形计数器及模值2n的扭环形计数器。

序列信号发生器

一般分为移存型序列信号发生器和计数型序列信号发生器。

移存型序列信号发生器

移存型序列信号发生器一般由移位寄存器和组合反馈电路构成,设计方法:

- 首先根据序列信号长度,确定最少触发器数目n,对于计数型序列信号发生器,须满足:

- 通过分组,验证n是否满足需要(若分组中有重复的,则需要验证n+1个触发器)

- 按编码编写状态转移表,状态转移表最后一列即为反馈信号D

- 求反馈函数D并化简

- 检查电路自启动,画出逻辑图。

计数型序列信号发生器

计数型序列信号发生器的输出位于组合输出电路,另外不用验证自启动,其最大的优点是可以同时产生多个序列。

例如下图,可以产生10101、11011两种序列: